在设计中使用超高速数据转换器的高速应用通常需要非常干净的时钟信号,以确保外部时钟源不会对系统的整体动态性能产生不希望的噪声.因此,选择合适的系统组件至关重要,这有助于产生低相位抖动时钟.以下应用笔记是选择适当元件以设计基于PLL的低相位噪声晶体振荡器的有价值指南,适用于超高速数据转换器.

许多现代,高速,高性能的集成电路,如MAX104和MAX106模数转换器(ADC),需要一个工作在GHz范围内的低相位噪声(低抖动)时钟.传统的石英晶体振荡器可以提供低抖动时钟信号,但通常不能在120MHz以上的振荡频率下使用.

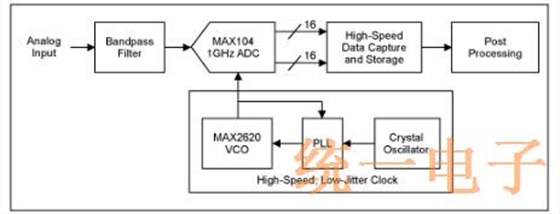

图1示出了典型的高速数据转换器系统的简化框图.该系统由带通滤波器,ADC,高频时钟,高速存储设备和后处理单元组成.除MAX104外,高频时钟在确定高速数据转换器的精度方面起着重要作用.这种高频,低相位噪声时钟是高频压控振荡器(U1),锁相环(U2)和晶体振荡器(U3)的组合,如图2所示.

图1.使用MAX104 ADC和基于PLL的低抖动晶体振荡器的典型高速数据转换器系统.

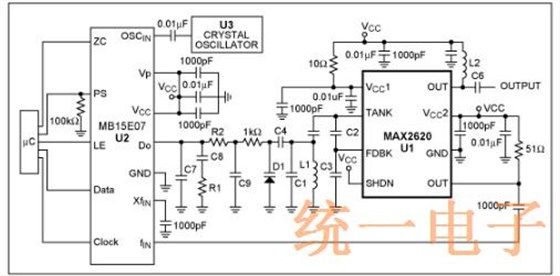

图2.高速,低相位噪声时钟是确保高速ADC最佳动态性能的最关键因素之一.

MAX2620压控振荡器(VCO)能够产生高达1GHz的振荡器频率,同时提供足够的噪声性能.由于固有的频率漂移,通常需要锁相环(PLL)通过将VCO输出与有源晶体振荡器频率进行比较来将VCO输出锁定到所需频率.

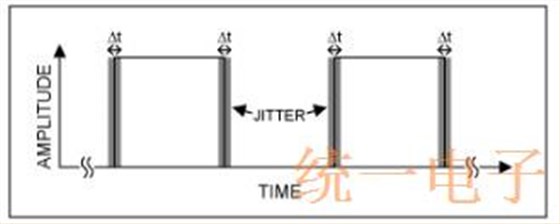

为高速数据转换器系统选择合适的VCXO晶体振荡器并不像找到具有正确振荡器频率的VCO那么简单.必须考虑的一个关键参数是时钟抖动.抖动通常被定义为数字信号从其理想位置的重要瞬间的短期非累积变化.图3示了包含抖动的采样时钟信号.时钟产生的抖动是由各种内部噪声源引起的,例如热噪声,相位噪声和杂散噪声.在数据转换器的情况下,抖动会影响数据转换器的信噪比(SNR)性能.

图3.时钟信号中的抖动会降低ADC的信噪比.

时钟抖动如何降低ADC的信噪比(SNR)

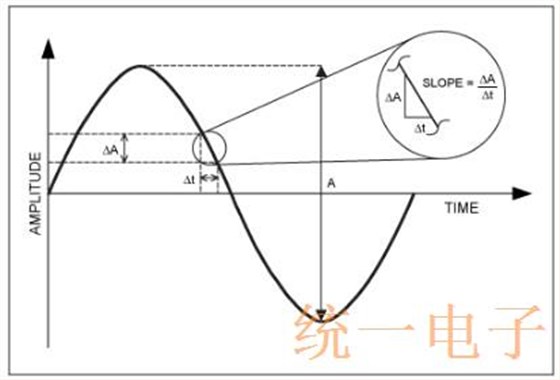

时钟源产生的抖动可能导致ADC的内部电路错误地触发采样时间.如图4所示,采样时间Δt的不确定性等于幅度ΔA的不确定性.这导致模拟输入幅度的错误采样,从而降低ADC的SNR.通过以下等式,可以针对给定量的时钟抖动计算数据转换器的最大SNR:

图4.使用采样时间不确定性获得的SNR模型.

当cos(ωt)项为1时,斜率处于最大值.因此,

EQ.2可以重新排列为:

根据定义,A/(ΔA)是信噪比,Δt是抖动的均方根(RMS)值.EQ.3可以改写为:

例如,如果模拟输入信号是250MHz晶振的,为50dB SNR是要达到,最大RMS抖动(σRMS)必须小于2PS.

噪声源如何引起抖动

热噪声,频率调制(FM),幅度调制(AM),相位调制(PM)和杂散成分会导致导致有源晶振信号抖动的噪声.由于难以区分由FM,AM和PM引起的噪声,所有三种类型的噪声被分组为称为相位噪声的通用术语.

NDK晶振,谐振器,石英晶振,NX2016SA晶振

NDK晶振,谐振器,石英晶振,NX2016SA晶振 NDK晶振,谐振器,石英晶振,NX1612SA晶振

NDK晶振,谐振器,石英晶振,NX1612SA晶振 NDK晶振,谐振器,贴片晶振,NX3225GA晶振

NDK晶振,谐振器,贴片晶振,NX3225GA晶振 NDK晶振,谐振器,贴片晶振,NX1210AB晶振

NDK晶振,谐振器,贴片晶振,NX1210AB晶振